Synopsys全新基于FPGA的原型驗證解決方案將系統性能提升高達3倍

亮點:

· 借助增強型HapsTrak 3 I/O連接器技術以及高速時域多路復用技術,使系統性能提升高達3倍

· 模塊化系統架構可覆蓋從1200萬到1.44億個專用集成電路門,以適用于從單個IP單元到處理器子系統再到完整SoC的各種規模的設計

· Synopsys Certify®軟件中的新功能與HAPS靈活的互連架構相結合,將多FPGA分區的產能加速高達10倍

· 增強的UMR總線(Universal Multi-Resource Bus)帶寬高達400MB/s,有助于提升糾錯的能力,并與Synopsys的Virtualizer工具一起,提升混合原型驗證的性能。

· 經過預先驗證的Synopsys DesignWare® IP與HAPS系統一起可確保IP單元的高效集成和更早的軟件開發

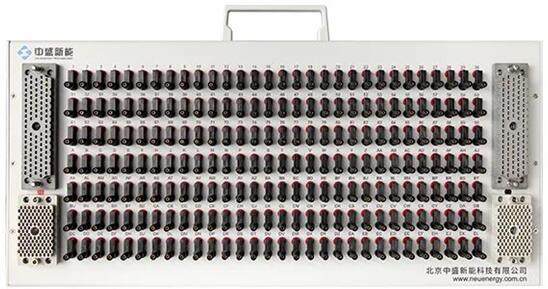

提供應用于芯片和電子系統加速創新的軟件、知識產權(IP)及服務的全球性領先供應商新思科技公司(Synopsys, Inc., 納斯達克股票市場代碼:SNPS)日前宣布:該公司推出其Synopsys HAPS®-70系列基于FPGA的原型驗證系統,從而擴展了其HAPS產品線以應對系統級芯片(SoC)設計的不斷增加的規模及復雜度。HAPS-70系統提供了緊密集成的原型驗證軟件和硬件,包括高速時域多路復用(HSTDM)技術,它與新的HapsTrak 3 I/O連接器相結合可提供比傳統的連接器和引腳復用技術高出可達3倍的原型性能改進。此款新的原型系統利用了一個可擴展的架構以及較新一代的賽靈思Virtex-7 FPGA器件,以支持范圍廣泛的、各種大小的設計,其容量可從1200萬到1.44億個專用集成電路(ASIC)門。Virtex-7’s I/O bank和HapsTrak 3連接器之間的靈活性及匹配的引腳連接,使HAPS用戶能夠將I/O帶寬用在較需要的地方,同時使未用管腳的數量減至較少。

了解多媒體新聞稿,請訪問:

http://www.synopsys.com/Company/PressRoom/Pages/haps70-news-release.aspx

“Virtex-7 2000T FPGA的堆疊硅片互聯技術可提供兩百萬個邏輯單元的容量以及12.5 Gb/s的串行收發器,使其可以理想地被用于需要大容量和高速I/O的ASIC原型,”賽靈思FPGA平臺市場營銷副總裁Tim Erjavec說道。“Synopsys的HAPS-70系列利用了Virtex-7 2000T FPGA增大的設計容量和I/O bank結構,提供了一種可以在FPGA內部和多個FPGA之間簡化設計規劃的系統,同時使HAPS-70可以擴展到支持數百萬ASIC門的SoC設計。”

HAPS-70系統與一種智能原型驗證軟件環境集成在一起,可實現更快速地分區以及自動地為各種規模設計進行原型生成和糾錯,包括從單個的IP單元和處理器子系統再到完整的SoC,從而簡化了從RTL到可運行原型的途徑。HAPS-70系統的模塊化架構使工程師能夠使用通用的原型環境來進行IP和SoC軟件開發、軟/硬件集成和系統驗證,從而減少了不同項目間的重復工作量。Synopsys的Certify多FPGA原型驗證軟件的全新“HAPS感知”功能借助正在申請專利的算法可將原型驗證生產力提高10倍,該功能自動進行邏輯分區和現場硬件查詢,與手動的分區方法相比簡化了系統的形成。此款新的原型驗證系統還支持HAPS深度追蹤糾錯(HAPS Deep Trace Debug)功能以實現更高的糾錯效率,與FPGA片上型邏輯糾錯器上使用的傳統存儲器相比,存儲容量提升了將近100倍。

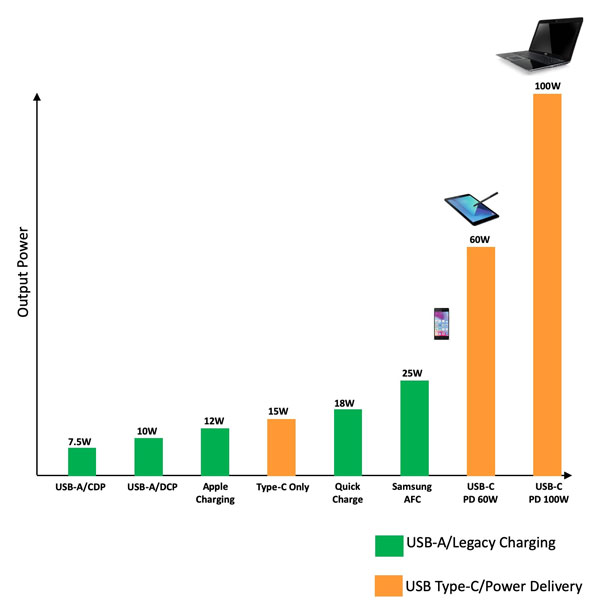

為了實現更容易的系統驗證和軟件開發,諸如USB 3.0、PCI Express®和HDMI 那樣的DesignWare接口IP都在HAPS系統上已經進行了驗證。憑借在HAPS系統上經過預先驗證的DesignWare IP以及用于通用IP協議的子卡的豐富可選性,設計師可以在產品開發周期中能夠更早地著手軟件開發,并且減少了IP集成的工作量。

“Synopsys 的HAPS基于FPGA的原型驗證解決方案,在加速我們的硬件/軟件驗證以及提高我們的原型驗證產能方面,對Mindspeed起到了不可估量的作用,”敏迅科技(Mindspeed Technologies)公司VLSI Core Engineering執行總監Surinder Dhaliwal說道。“由于我們在不斷地開發基礎設施產品解決方案,因此我們很高興Synopsys已經針對像我們產品那樣更大規模、更復雜設計加強了其基于FPGA的原型驗證系列,使它們具有更高性能、更大容量以及改善的糾錯可見度。”

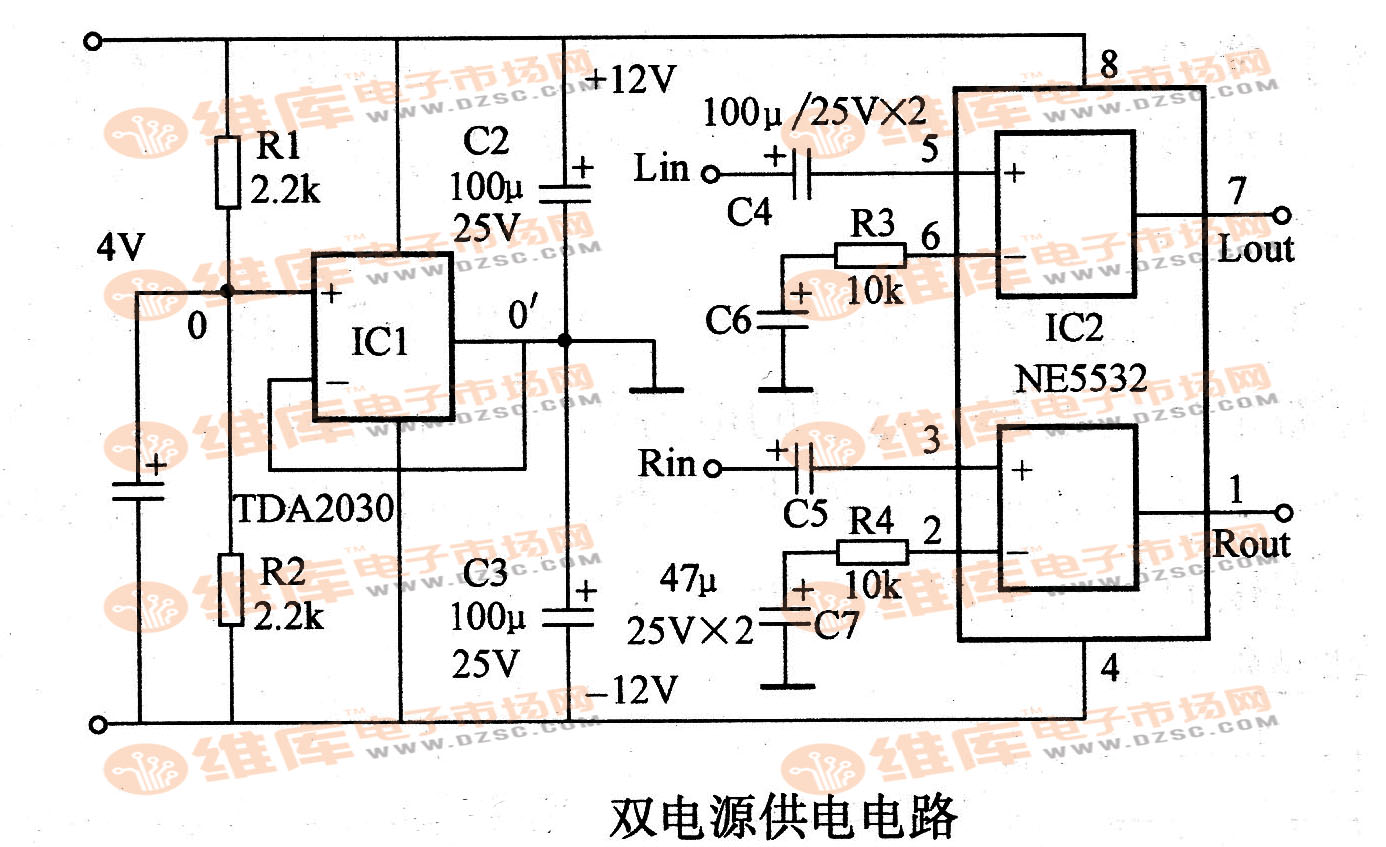

Synopsys的針對HAPS-70系統的UMRBus功能已被加強,可支持高達400 MB/s的帶寬。UMRBus在HAPS-70系統和Synopsys的基于Virtualizer的虛擬原型之間提供了無縫連接,為早期的軟件開發和軟/硬件集成創造了一個集成化混合原型驗證環境。UMRBus還可提供遠程訪問,通用的C++/TCL編程接口, 與Synopsys的VCS®功能驗證解決方案一起進行co-simulation, 該 co-simulation 使層次化的模塊級啟動與糾錯成為可能,UMRBUS的這些特性使HAPS-70系統可以更早地被納入到設計流程。

“日益增長的設計規模、軟件復雜度和盡可能早的軟件開發都成為了SoC原型設計師的關鍵挑戰,” Synopsys IP與系統市場營銷副總裁John Koeter說道。“通過提供業界領先的、基于 FPGA的原型容量和性能,以及借助智能分區和糾錯工具,HAPS-70系統所擴展的功能進一步縮短了軟件開發和軟/硬件集成的時間。通過發揮我們全面的硬件、軟件和IP技術領先性,設計師們在驗證他們較大規模的芯片設計時會立顯成效。”

供貨&資源

HAPS-70基于FPGA的原型驗證系統現已可向早期采用者提供9種型號的產品系列,容量從1200萬到1.44億個ASIC門:HAPS-70 S12、HAPS-70 S24、HAPS-70 S36、HAPS-70 S48、HAPS-70 S60、HAPS-70 S72、HAPS-70 S96、HAPS-70 S120和HAPS-70 S144,其中S是指可支持的ASIC門數。

了解更多關于HAPS-70: http://www.synopsys.com/haps70.

o 混合原型設計:http://www.synopsys.com/Systems/fpga_hybrid

o HAPS糾錯:http://www.synopsys.com/Systems/HAPS_DTD

o 基于FPGA的原型驗證方法指南:http://www.synopsys.com/Systems/FPMM

o 基于FPGA的原型驗證博客:http://blogs.synopsys.com/breakingthethreelaws/

HAPS-70基于FPGA的原型解決方案將參加“2012嵌入式技術/電子設計解決方案展覽會”:Synopsys將在嵌入式技術/電子設計解決方案展覽會上展示其運行于HAPS-70硬件上的較新基于FPGA的原型驗證解決方案,展位號:# D-35。ET / EDS展覽會于2012年11月14日-16日在日本橫濱舉辦。更多關于Synopsys參加2012 ET / EDS展覽會信息請訪問:http://www.jasa.or.jp/et/ET2012/english/index.html

關于Synopsys

Synopsys(Nasdaq:SNPS)加速了全球電子市場中的創新。作為一家電子設計自動化(EDA)和半導體IP領域內的領導者,其軟件、IP和服務幫助工程師應對設計、驗證、系統和制造中的各種挑戰。自1986年以來,全世界的工程師使用Synopsys的技術已經設計和創造了數十億個芯片和系統。更多信息請登錄http://www.synopsys.com.

相關閱讀:

- ...2018/01/24 17:29·Arteris IP和Synopsys促進神經網絡 和異構多核系統級芯片的優化

- ...2016/08/03 10:42·面向英飛凌新一代TriCore架構的Synopsys全新模型 可加快早期汽車軟件開發和測試

- ...2016/06/03 08:45·愛普生和美高森美合作提供IEEE 1588-2008和SyncE合規網絡 同步解決方案,用于快速擴展的分組網絡基礎設施

- ...2016/02/04 10:15·Synopsys推出全新IP子系統以加速物聯網設備中的數據融合處理

- ...2016/02/01 21:04·Synopsys的Platform Architect MCO提供業界首套支持IEEE 1801-2015 UPF 3.0的功耗感知架構分析工具

- ...2016/01/28 11:07·Synopsys推出SiliconSmart ADV單元庫特性表征解決方案

- ...· Efinix® 全力驅動AI邊緣計算,成功推出Trion™ T20 FPGA樣品, 同時將產品擴展到二十萬邏輯單元的T200 FPGA

- ...· 英飛凌亮相進博會,引領智慧新生活

- ...· 三電產品開發及測試研討會北汽新能源專場成功舉行

- ...· Manz亞智科技跨入半導體領域 為面板級扇出型封裝提供化學濕制程、涂布及激光應用等生產設備解決方案

- ...· 中電瑞華BITRODE動力電池測試系統順利交付北汽新能源

- ...· 中電瑞華FTF系列電池測試系統中標北京新能源汽車股份有限公司

- ...· 中電瑞華大功率高壓能源反饋式負載系統成功交付中電熊貓

- ...· 中電瑞華國際在電動汽車及關鍵部件測評研討會上演繹先進測評技術