得可提升DirEKt Coat技術高度

具有涂敷25微米厚的涂層至150微米薄的晶圓上的能力,DirEKt Coat晶圓背覆涂層技術使加工時間更快并使芯片封裝尺寸較大化。傳統如涂敷的芯片粘合劑工藝,已不能提供當今大批量制造所需的速度和涂敷精度。不均勻的粘合劑覆蓋、由于樹脂溢出和芯片四周帶狀成形導致芯片封裝尺寸的限制、及較慢的連續涂敷速度是傳統芯片貼合工藝固有和眾所周知的問題。而DirEKt Coat能在已獲認可的印刷設備上提供并行處理,于一個行程內在200毫米大的晶圓上進行材料涂敷,并十倍提升加工速度。而且,粘合劑層達到客戶規格,而芯片四周帶狀成形予以清除,提供更具功能性的更大芯片面積。

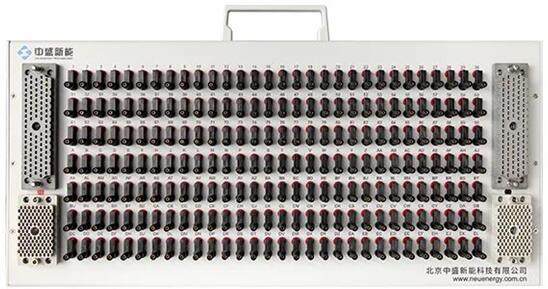

DirEKt Coat工藝能力的提升關鍵,是得可的全新Galaxy薄晶圓系統,其包括穩健的軌道和精密的輸送技術,及容納全新設計的下一代晶圓托盤。獨有多孔材料設計的托盤,確保薄晶圓在采用得可任一公認半導體封裝工藝進行印刷時保持固定和穩定。托盤平整度小于10微米,400毫米見方,能容納直徑達300毫米、厚度為75微米的晶圓。托盤獨有的平整度和系統的穩定性確保Cp的提高和杰出的7微米總厚度差。

“伴隨產品小型化和增強功能的不變進程,當今的經濟形勢正迫使封裝公司更多地利用其工藝。”得可半導體和可替代應用經理David Foggie說:“而我們在貫徹得可‘期待更多’的宗旨和履行技術引領地位的承諾方面,已經賦予DirEKt Coat適用于未來的工藝,提供薄晶圓應用更好的性能、更強的穩定性和更快的加工速度,而所有這些相比目前的芯片貼合薄膜產品,減少了30%的材料成本。”

值得一提的是,對DirEKt Coat晶圓背覆涂層工藝的改進并未損失其原有的任何優勢,包括由于芯片四周帶狀成形消除使所需粘合劑量的減少、預生產和儲存晶圓以應對隨時需求的能力、以及相對于采購不同厚度和寬度的薄膜產品,使用單一材料滿足多種需求所獲得的供應鏈效率的提升。

Galaxy薄晶圓系統能進行其他各種先進的半導體工藝,包括但并不限于DirEKt Ball Placement、熱界面材料涂敷、晶圓凸起和密封劑涂敷。想要了解更多,請聯系DEK。

相關閱讀:

- ...· Efinix® 全力驅動AI邊緣計算,成功推出Trion™ T20 FPGA樣品, 同時將產品擴展到二十萬邏輯單元的T200 FPGA

- ...· 英飛凌亮相進博會,引領智慧新生活

- ...· 三電產品開發及測試研討會北汽新能源專場成功舉行

- ...· Manz亞智科技跨入半導體領域 為面板級扇出型封裝提供化學濕制程、涂布及激光應用等生產設備解決方案

- ...· 中電瑞華BITRODE動力電池測試系統順利交付北汽新能源

- ...· 中電瑞華FTF系列電池測試系統中標北京新能源汽車股份有限公司

- ...· 中電瑞華大功率高壓能源反饋式負載系統成功交付中電熊貓

- ...· 中電瑞華國際在電動汽車及關鍵部件測評研討會上演繹先進測評技術