Altera Stratix V GX FPGA實現了與PCIe Gen3的兼容,名列PCI-SIG Integrators名錄

Altera產品營銷資深總監Patrick Dorsey評論說:“Stratix V FPGA被PCIe Gen 3 Integrators名錄收錄表明我們的高性能器件非常成功。高性能Stratix V和PCIe Gen3能夠一起無縫工作,需要它們的客戶現在可以充滿信心的設計系統。此外,我們新的DMA參考設計簡化并加速了高性能PCIe Gen3x8硬件的開發。”

Altera DMA參考設計重點突出了需要PCIe Gen3x8的Stratix V設計的功能。通過展示理論較大峰值帶寬,參考設計表明Altera的Gen3解決方案幾乎能夠實現Gen3系統的全部帶寬,或者Gen3數據速率。而且,通過展示高達11 GB/秒的同時讀/寫操作,設計顯示了客戶在實際實現時能夠使用多大帶寬。DMA參考設計的特性包括:

· 與實例設計一同工作的Linux驅動

· 峰值吞吐量(250MHz時,256位142周期)

· 7.1 GB/s:背靠背Tx存儲器寫256字節負載

· 7.0 GB/s:背靠背Rx讀完成吞吐量

· 同時讀/寫操作:11.4GB/秒

面向PCIe Gen3的Altera Stratix V GX FPGA

Stratix V FPGA具有四個硬核PCIe Gen3x8知識產權(IP)模塊。PCIe Gen3 IP模塊支持x1、x2、x4和x8通路配置,每個通路傳送速率高達8-Gbps,與前一版本的Gen2 x8相比,使用Gen3 x8通路,吞吐量提高了兩倍。與相應的軟核實施方案相比,Stratix V FPGA中的PCIe IP硬核模塊節省了100,000多個邏輯單元。硬核PCIe Gen3 IP模塊將PCIe協議堆棧嵌入到FPGA中,包括了收發器模塊、物理層、數據鏈路層和會話層。Stratix V FPGA的PCIe Gen3 IP面向PCIe基本規范Rev 3.0、2.x和1.x。

Altera提供其全系列產品全面的PCI-SIG兼容解決方案,這些產品經過優化滿足了關鍵應用需求。這些解決方案包括支持端點、橋接、交換和根端口功能的可配置PCIe IP內核和開發板。

供貨信息

Altera Stratix V GX FPGA目前已經開始成品發售。Quartus® II軟件13.0版下載中提供DMA參考設計。

如果有其他問題,或者需要了解訂購信息,請聯系您當地的Altera銷售代表或者授權代理商。

Altera簡介

Altera®的可編程解決方案幫助電子系統設計人員快速高效地實現創新,突出產品優勢,贏得市場競爭。Altera提供FPGA、SoC、CPLD和ASIC以及軟件工具、知識產權、嵌入式處理器和客戶支持,為全世界客戶提供高價值可編程解決方案。請通過Facebook、Twitter、LinkedIn、Google+和RSS關注Altera,訂閱產品更新電子郵件和新聞快報。

相關閱讀:

- ...2018/01/16 16:52·賽普拉斯PSoC6 MCU助力Oura Health創新型可穿戴健康產品橫空出世

- ...2018/01/16 16:52·賽普拉斯PSoC6 MCU助力Oura Health創新型可穿戴健康產品橫空出世

- ...2016/11/17 19:42·Altium全新版本PCB設計軟件亮相助力用戶實現激情設計

- ...2016/11/15 10:48·Altium發布全新劃時代PCB設計與數據管理技術

- ...2016/10/20 12:29·Altium發布基于較新AURIX™技術的TASKING VX-toolset for TriCore™重要更新

- ...2016/05/04 09:27·Altera設計解決方案網絡連接客戶和專家,助力客戶基于FPGA的設計創新

- ...· Efinix® 全力驅動AI邊緣計算,成功推出Trion™ T20 FPGA樣品, 同時將產品擴展到二十萬邏輯單元的T200 FPGA

- ...· 英飛凌亮相進博會,引領智慧新生活

- ...· 三電產品開發及測試研討會北汽新能源專場成功舉行

- ...· Manz亞智科技跨入半導體領域 為面板級扇出型封裝提供化學濕制程、涂布及激光應用等生產設備解決方案

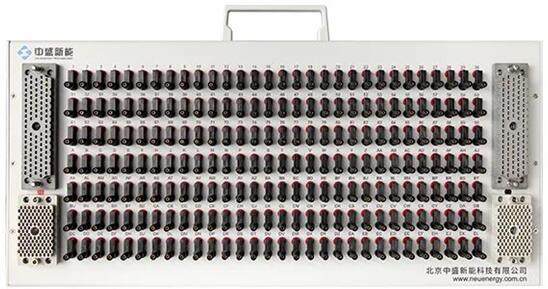

- ...· 中電瑞華BITRODE動力電池測試系統順利交付北汽新能源

- ...· 中電瑞華FTF系列電池測試系統中標北京新能源汽車股份有限公司

- ...· 中電瑞華大功率高壓能源反饋式負載系統成功交付中電熊貓

- ...· 中電瑞華國際在電動汽車及關鍵部件測評研討會上演繹先進測評技術